# The Turtles Project: Design and Implementation of Nested Virtualization

<u>Muli Ben-Yehuda</u><sup>†</sup> Michael D. Day<sup>‡</sup> Zvi Dubitzky<sup>†</sup> Michael Factor<sup>†</sup> Nadav Har'El<sup>†</sup> Abel Gordon<sup>†</sup> Anthony Liguori<sup>‡</sup> Orit Wasserman<sup>†</sup> Ben-Ami Yassour<sup>†</sup>

<sup>†</sup>IBM Research – Haifa

<sup>‡</sup>IBM Linux Technology Center

#### What is nested x86 virtualization?

- Running multiple unmodified hypervisors

- With their associated unmodified VM's

- Simultaneously

- On the x86 architecture

- Which does not support nesting in hardware...

- ... but does support a single level of virtualization

- Operating systems are already hypervisors (Windows 7 with XP mode, Linux/KVM)

- To be able to run other hypervisors in clouds

- Security (e.g., hypervisor-level rootkits)

- Co-design of x86 hardware and system software

- Testing, demonstrating, debugging, live migration of hypervisors

- Operating systems are already hypervisors (Windows 7 with XP mode, Linux/KVM)

- To be able to run other hypervisors in clouds

- Security (e.g., hypervisor-level rootkits)

- Co-design of x86 hardware and system software

- Testing, demonstrating, debugging, live migration of hypervisors

- Operating systems are already hypervisors (Windows 7 with XP mode, Linux/KVM)

- To be able to run other hypervisors in clouds

- Security (e.g., hypervisor-level rootkits)

- Co-design of x86 hardware and system software

- Testing, demonstrating, debugging, live migration of hypervisors

- Operating systems are already hypervisors (Windows 7 with XP mode, Linux/KVM)

- To be able to run other hypervisors in clouds

- Security (e.g., hypervisor-level rootkits)

- Co-design of x86 hardware and system software

- Testing, demonstrating, debugging, live migration of hypervisors

- Operating systems are already hypervisors (Windows 7 with XP mode, Linux/KVM)

- To be able to run other hypervisors in clouds

- Security (e.g., hypervisor-level rootkits)

- Co-design of x86 hardware and system software

- Testing, demonstrating, debugging, live migration of hypervisors

• First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

- First models for nested virtualization [PopekGoldberg74, BelpaireHsu75, LauerWyeth73]

- First implementation in the IBM z/VM; relies on architectural support for nested virtualization (sie)

- Microkernels meet recursive VMs [FordHibler96]: assumes we can modify software at all levels

- x86 software based approaches (slow!) [Berghmans10]

- KVM [KivityKamay07] with AMD SVM [RoedelGraf09]

- Early Xen prototype [He09]

- Blue Pill rootkit hiding from other hypervisors [Rutkowska06]

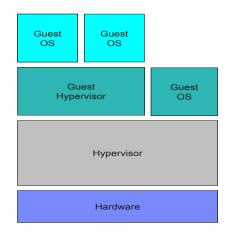

# What is the Turtles project?

- Efficient nested virtualization for Intel x86 based on KVM

- Runs multiple guest hypervisors and VMs: KVM, VMware, Linux, Windows, ...

- Code publicly available

| _ | _ | _ | <br>_ |

|---|---|---|-------|

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

|   |   |   |       |

#### Nested VMX virtualization for nested CPU virtualization

- Multi-dimensional paging for nested MMU virtualization

- Multi-level device assignment for nested I/O virtualization

- Micro-optimizations to make it go fast

- Nested VMX virtualization for nested CPU virtualization

- Multi-dimensional paging for nested MMU virtualization

- Multi-level device assignment for nested I/O virtualization

- Micro-optimizations to make it go fast

- Nested VMX virtualization for nested CPU virtualization

- Multi-dimensional paging for nested MMU virtualization

- Multi-level device assignment for nested I/O virtualization

- Micro-optimizations to make it go fast

- Nested VMX virtualization for nested CPU virtualization

- Multi-dimensional paging for nested MMU virtualization

- Multi-level device assignment for nested I/O virtualization

- Micro-optimizations to make it go fast

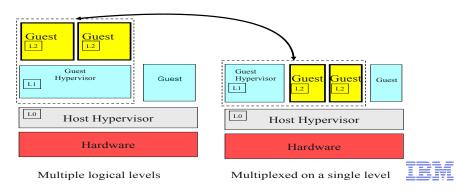

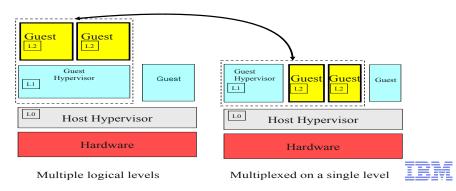

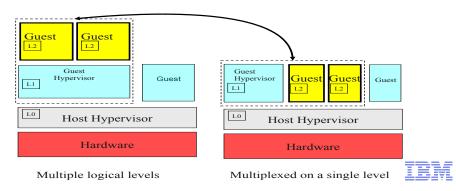

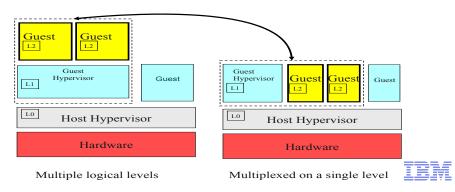

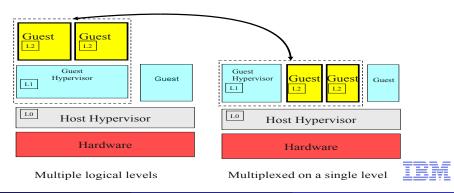

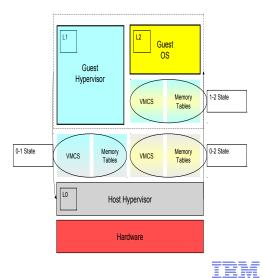

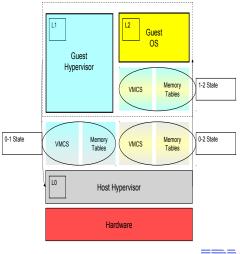

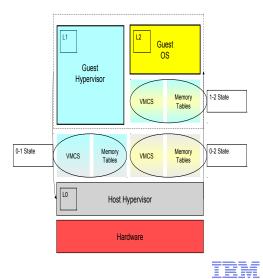

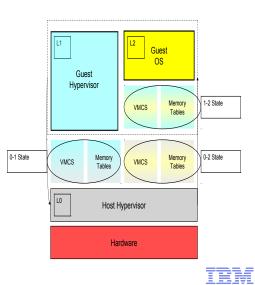

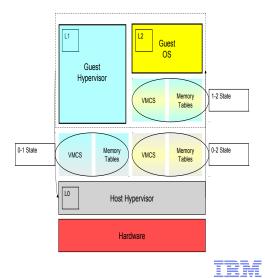

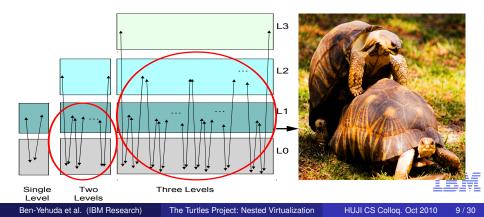

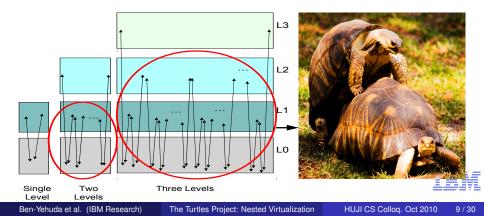

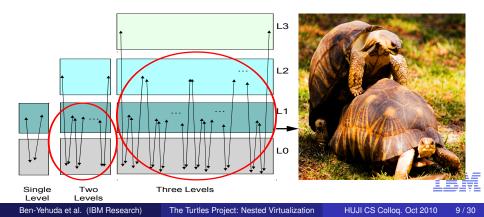

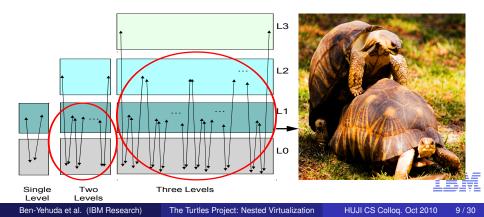

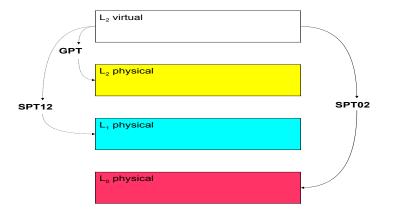

#### • Trap and emulate[PopekGoldberg74] ⇒ it's all about the traps

- Single-level (x86) vs. multi-level (e.g., z/VM)

- Single level ⇒ one hypervisor, many guests

- Turtles approach: L<sub>0</sub> multiplexes the hardware between L<sub>1</sub> and L<sub>2</sub>, running both as guests of L<sub>0</sub>—without either being aware of it

- (Scheme generalized for n levels; Our focus is n=2)

- Trap and emulate[PopekGoldberg74]  $\Rightarrow$  it's all about the traps

- Single-level (x86) vs. multi-level (e.g., z/VM)

- Single level ⇒ one hypervisor, many guests

- Turtles approach: L<sub>0</sub> multiplexes the hardware between L<sub>1</sub> and L<sub>2</sub>, running both as guests of L<sub>0</sub>—without either being aware of it

- (Scheme generalized for n levels; Our focus is n=2)

- Trap and emulate[PopekGoldberg74] ⇒ it's all about the traps

- Single-level (x86) vs. multi-level (e.g., z/VM)

- Single level ⇒ one hypervisor, many guests

- Turtles approach: L<sub>0</sub> multiplexes the hardware between L<sub>1</sub> and L<sub>2</sub>, running both as guests of L<sub>0</sub>—without either being aware of it

- (Scheme generalized for n levels; Our focus is n=2)

- Trap and emulate[PopekGoldberg74]  $\Rightarrow$  it's all about the traps

- Single-level (x86) vs. multi-level (e.g., z/VM)

- Single level ⇒ one hypervisor, many guests

- Turtles approach: L<sub>0</sub> multiplexes the hardware between L<sub>1</sub> and L<sub>2</sub>, running both as guests of L<sub>0</sub>—without either being aware of it

- (Scheme generalized for n levels; Our focus is n=2)

- Trap and emulate[PopekGoldberg74] ⇒ it's all about the traps

- Single-level (x86) vs. multi-level (e.g., z/VM)

- Single level  $\Rightarrow$  one hypervisor, many guests

- Turtles approach: L<sub>0</sub> multiplexes the hardware between L<sub>1</sub> and L<sub>2</sub>, running both as guests of L<sub>0</sub>—without either being aware of it

- (Scheme generalized for n levels; Our focus is n=2)

Ben-Yehuda et al. (IBM Research) The Turtles Project: Nested Virtualization HUJI CS Colloq. Oct 2010 7 / 30

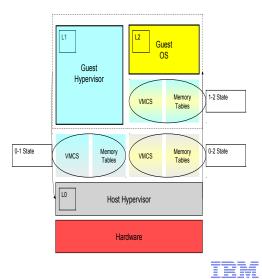

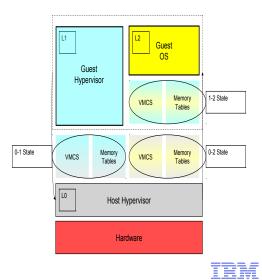

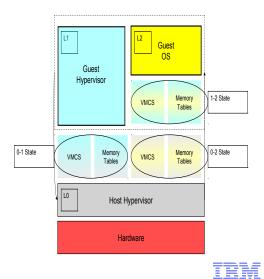

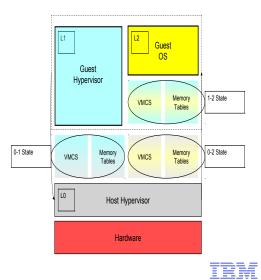

#### • $L_0$ runs $L_1$ with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- L<sub>0</sub> merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- L<sub>0</sub> merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- L<sub>0</sub> merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

Ben-Yehuda et al. (IBM Research)

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

```

• eventually, L<sub>0</sub> resumes L<sub>2</sub>

```

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- ...

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

#### repeat

- $L_0$  runs  $L_1$  with VMCS<sub>0 $\rightarrow 1$ </sub>

- L<sub>1</sub> prepares VMCS<sub>1→2</sub> and executes vmlaunch

- vmlaunch traps to L<sub>0</sub>

- $L_0$  merges VMCS's: VMCS<sub>0→1</sub> merged with VMCS<sub>1→2</sub> is VMCS<sub>0→2</sub>

- L<sub>0</sub> launches L<sub>2</sub>

- L<sub>2</sub> causes a trap

- L<sub>0</sub> handles trap itself or forwards it to L<sub>1</sub>

- . . .

- eventually, L<sub>0</sub> resumes L<sub>2</sub>

- repeat

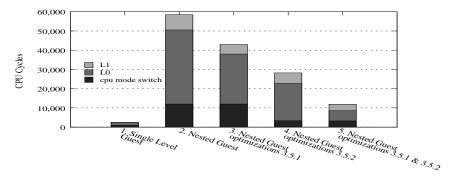

#### Exit multiplication makes angry turtle angry

- To handle a single L<sub>2</sub> exit, L<sub>1</sub> does many things: read and write the VMCS, disable interrupts, ...

- Those operations can trap, leading to exit multiplication

- Exit multiplication: a single L<sub>2</sub> exit can cause 40-50 L<sub>1</sub> exits!

- Optimize: make a single exit fast and reduce frequency of exits

#### Exit multiplication makes angry turtle angry

- To handle a single L<sub>2</sub> exit, L<sub>1</sub> does many things: read and write the VMCS, disable interrupts, ...

- Those operations can trap, leading to exit multiplication

- Exit multiplication: a single L<sub>2</sub> exit can cause 40-50 L<sub>1</sub> exits!

- Optimize: make a single exit fast and reduce frequency of exits

### Exit multiplication makes angry turtle angry

- To handle a single L<sub>2</sub> exit, L<sub>1</sub> does many things: read and write the VMCS, disable interrupts, ...

- Those operations can trap, leading to exit multiplication

- Exit multiplication: a single L<sub>2</sub> exit can cause 40-50 L<sub>1</sub> exits!

- Optimize: make a single exit fast and reduce frequency of exits

### Exit multiplication makes angry turtle angry

- To handle a single L<sub>2</sub> exit, L<sub>1</sub> does many things: read and write the VMCS, disable interrupts, ...

- Those operations can trap, leading to exit multiplication

- Exit multiplication: a single L<sub>2</sub> exit can cause 40-50 L<sub>1</sub> exits!

- Optimize: make a single exit fast and reduce frequency of exits

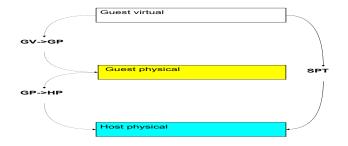

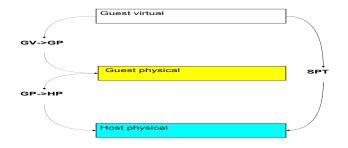

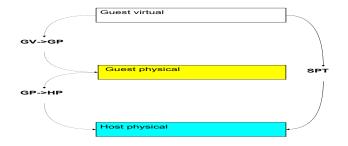

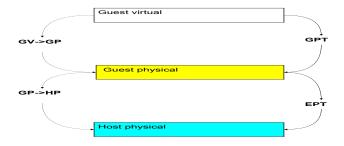

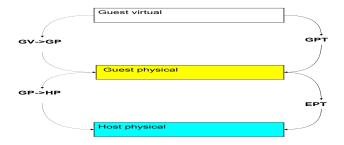

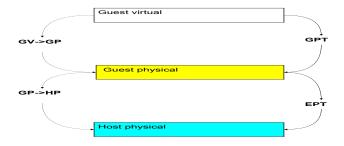

#### • x86 does page table walks in hardware

- MMU has one currently active hardware page table

- Bare metal ⇒ only needs one logical translation, (virtual → physical)

- Virtualization  $\Rightarrow$  needs two logical translations

- I Guest page table: (guest virt  $\rightarrow$  guest phys)

- 2 Host page table: (guest phys  $\rightarrow$  host phys)

- ... but MMU only knows to walk a single table!

- x86 does page table walks in hardware

- MMU has one currently active hardware page table

- Bare metal ⇒ only needs one logical translation, (virtual → physical)

- Virtualization  $\Rightarrow$  needs two logical translations

- I Guest page table: (guest virt  $\rightarrow$  guest phys)

- 2 Host page table: (guest phys  $\rightarrow$  host phys)

- ... but MMU only knows to walk a single table!

- x86 does page table walks in hardware

- MMU has one currently active hardware page table

- Bare metal ⇒ only needs one logical translation, (virtual → physical)

- Virtualization  $\Rightarrow$  needs two logical translations

- $\bigcirc$  Guest page table: (guest virt ightarrow guest phys)

- a Host page table: (guest phys  $\rightarrow$  host phys)

- ... but MMU only knows to walk a single table!

- x86 does page table walks in hardware

- MMU has one currently active hardware page table

- Bare metal ⇒ only needs one logical translation, (virtual → physical)

- Virtualization ⇒ needs two logical translations

- Ouest page table: (guest virt  $\rightarrow$  guest phys)

- 2 Host page table: (guest phys  $\rightarrow$  host phys)

- ... but MMU only knows to walk a single table!

- x86 does page table walks in hardware

- MMU has one currently active hardware page table

- Bare metal ⇒ only needs one logical translation, (virtual → physical)

- Virtualization ⇒ needs two logical translations

- Ouest page table: (guest virt  $\rightarrow$  guest phys)

- 2 Host page table: (guest phys  $\rightarrow$  host phys)

- ... but MMU only knows to walk a single table!

Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

- Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

- Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

- Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

- Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

- Two logical translations compressed onto the shadow page table [DevineBugnion02]

- Unmodified guest OS updates its own table

- Hypervisor traps OS page table updates

- Hypervisor propagates updates to the hardware table

- MMU walks the table

- Problem: traps are expensive

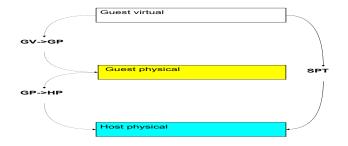

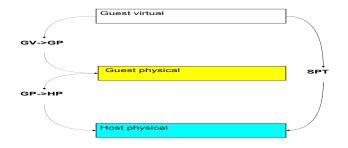

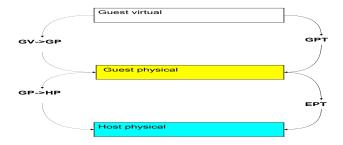

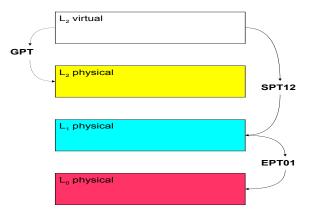

- Two-dimensional paging: guest owns GPT, hypervisor owns EPT [BhargavaSerebrin08]

- Unmodified guest OS updates GPT

- Hypervisor updates EPT table controlling (guest phys → host phys) translations

- MMU walks both tables

- Two-dimensional paging: guest owns GPT, hypervisor owns EPT [BhargavaSerebrin08]

- Unmodified guest OS updates GPT

- Hypervisor updates EPT table controlling (guest phys → host phys) translations

- MMU walks both tables

- Two-dimensional paging: guest owns GPT, hypervisor owns EPT [BhargavaSerebrin08]

- Unmodified guest OS updates GPT

- Hypervisor updates EPT table controlling (guest phys → host phys) translations

- MMU walks both tables

- Two-dimensional paging: guest owns GPT, hypervisor owns EPT [BhargavaSerebrin08]

- Unmodified guest OS updates GPT

- Hypervisor updates EPT table controlling (guest phys → host phys) translations

- MMU walks both tables

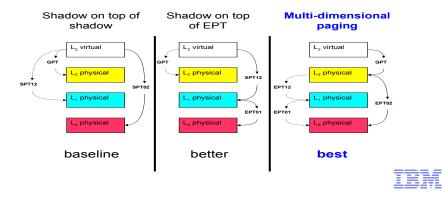

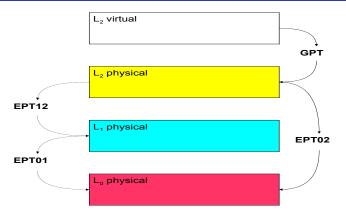

### Nested MMU virt. via multi-dimensional paging

- Three logical translations: L<sub>2</sub> virt  $\rightarrow$  phys, L<sub>2</sub>  $\rightarrow$  L<sub>1</sub>, L<sub>1</sub>  $\rightarrow$  L<sub>0</sub>

- Only two tables in hardware with EPT:

virt → phys and guest physical → host physical

- L<sub>0</sub> compresses three logical translations onto two hardware tables

### Baseline: shadow-on-shadow

- Assume no EPT table; all hypervisors use shadow paging

- Useful for old machines and as a baseline

- Maintaining shadow page tables is expensive

- Compress: three logical translations  $\Rightarrow$  one table in hardware

### Better: shadow-on-EPT

- Instead of one hardware table we have two

- Compress: three logical translations  $\Rightarrow$  two in hardware

- Simple approach: L<sub>0</sub> uses EPT, L<sub>1</sub> uses shadow paging for L<sub>2</sub>

- Every L<sub>2</sub> page fault leads to multiple L<sub>1</sub> exits

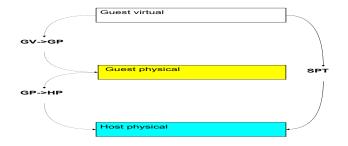

# Best: multi-dimensional paging

- EPT table rarely changes; guest page table changes a lot

- Again, compress three logical translations  $\Rightarrow$  two in hardware

- L<sub>0</sub> emulates EPT for L<sub>1</sub>

- $L_0$  uses  $\text{EPT}_{0 \rightarrow 1}$  and  $\text{EPT}_{1 \rightarrow 2}$  to construct  $\text{EPT}_{0 \rightarrow 2}$

- End result: a lot less exits!

Ben-Yehuda et al. (IBM Research)

The Turtles Project: Nested Virtualization

• From the hypervisor's perspective, what is I/O?

From the hypervisor's perspective, what is I/O?(1) PIO

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- Device emulation [Sugerman01]

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- Device emulation [Sugerman01]

• Para-virtualized drivers [Barham03, Russell08]

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- Device emulation [Sugerman01]

• Para-virtualized drivers [Barham03, Russell08]

• Direct device assignment [Levasseur04, Yassour08]

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- Device emulation [Sugerman01]

• Para-virtualized drivers [Barham03, Russell08]

Direct device assignment [Levasseur04, Yassour08]

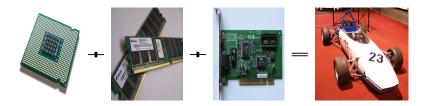

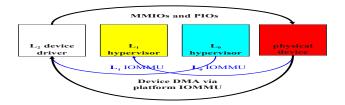

• Direct assignment best performing option

- From the hypervisor's perspective, what is I/O?

- (1) PIO (2) MMIO (3) DMA (4) interrupts

- Device emulation [Sugerman01]

• Para-virtualized drivers [Barham03, Russell08]

Direct device assignment [Levasseur04, Yassour08]

- Direct assignment best performing option

- Direct assignment requires IOMMU for safe DMA bypass

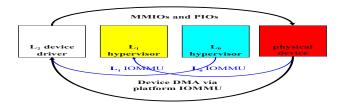

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

## Multi-level device assignment

- With nested 3x3 options for I/O virtualization ( $L_2 \Leftrightarrow L_1 \Leftrightarrow L_0$ )

- Multi-level device assignment means giving an L<sub>2</sub> guest direct access to L<sub>0</sub>'s devices, safely bypassing both L<sub>0</sub> and L<sub>1</sub>

- How? L<sub>0</sub> emulates an IOMMU for L<sub>1</sub> [Amit10]

- L<sub>0</sub> compresses multiple IOMMU translations onto the single hardware IOMMU page table

- L<sub>2</sub> programs the device directly

- Device DMA's into L<sub>2</sub> memory space directly

### Goal: reduce world switch overheads

- Reduce cost of single exit by focus on VMCS merges:

- Keep VMCS fields in processor encoding

- Partial updates instead of whole-sale copying

- Copy multiple fields at once

- Some optimizations not safe according to spec

- Reduce frequency of exits—focus on vmread and vmwrite

- Avoid the exit multiplier effect

- Loads/stores vs. architected trapping instructions

- Binary patching?

- Goal: reduce world switch overheads

- Reduce cost of single exit by focus on VMCS merges:

- Keep VMCS fields in processor encoding

- Partial updates instead of whole-sale copying

- Copy multiple fields at once

- Some optimizations not safe according to spec

- Reduce frequency of exits—focus on vmread and vmwrite

- Avoid the exit multiplier effect

- Loads/stores vs. architected trapping instructions

- Binary patching?

- Goal: reduce world switch overheads

- Reduce cost of single exit by focus on VMCS merges:

- Keep VMCS fields in processor encoding

- Partial updates instead of whole-sale copying

- Copy multiple fields at once

- Some optimizations not safe according to spec

- Reduce frequency of exits—focus on vmread and vmwrite

- Avoid the exit multiplier effect

- Loads/stores vs. architected trapping instructions

- Binary patching?

# Windows XP on KVM L<sub>1</sub> on KVM L<sub>0</sub>

Ben-Yehuda et al. (IBM Research)

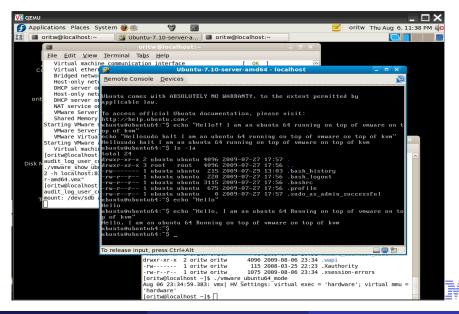

# Linux on VMware L<sub>1</sub> on KVM L<sub>0</sub>

Ben-Yehuda et al. (IBM Research)

# **Experimental Setup**

- Running Linux, Windows, KVM, VMware, SMP, ...

- Macro workloads:

- kernbench

- SPECjbb

- netperf

- Multi-dimensional paging?

- Multi-level device assignment?

- KVM as L<sub>1</sub> vs. VMware as L<sub>1</sub>?

See paper for full experimental details and more benchmarks and analysis

### Macro: SPECjbb and kernbench

| kernbench                       |              |                     |                 |                                |

|---------------------------------|--------------|---------------------|-----------------|--------------------------------|

|                                 | Host         | Guest               | Nested          | Nested <sub>DRW</sub>          |

| Run time                        | 324.3        | 355                 | 406.3           | 391.5                          |

| % overhead vs. host             | -            | 9.5                 | 25.3            | 20.7                           |

| % overhead vs. guest            | -            | -                   | 14.5            | <u>10.3</u>                    |

|                                 |              |                     | 1               | 1                              |

|                                 | SPEC         | jbb                 |                 |                                |

|                                 | SPEC<br>Host | jbb<br><b>Guest</b> | Nested          | Nested <sub>DRW</sub>          |

| Score                           |              | ,                   | Nested<br>77065 | Nested <sub>DRW</sub><br>78347 |

| Score<br>% degradation vs. host | Host         | Guest               |                 |                                |

Table: kernbench and SPECjbb results

- Exit multiplication effect not as bad as we feared

- Direct vmread and vmwrite (DRW) give an immediate boost

- Take-away: each level of virtualization adds approximately the same overhead!

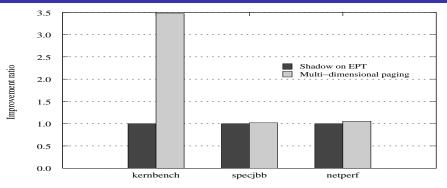

# Macro: multi-dimensional paging

- Impact of multi-dimensional paging depends on rate of page faults

- Shadow-on-EPT: every L<sub>2</sub> page fault causes L<sub>1</sub> multiple exits

- Multi-dimensional paging: only EPT violations cause L<sub>1</sub> exits

- EPT table rarely changes: #(EPT violations) << #(page faults)

- Multi-dimensional paging huge win for page-fault intensive kernbench

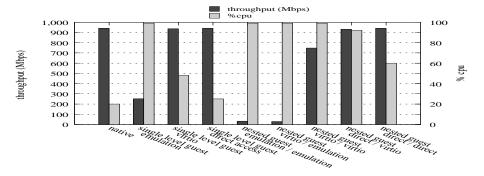

## Macro: multi-level device assignment

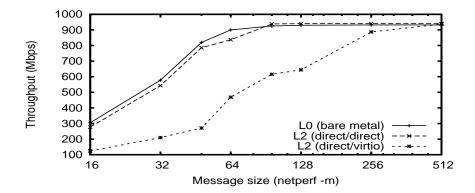

- Benchmark: netperf TCP\_STREAM (transmit)

- Multi-level device assignment best performing option

- But: native at 20%, multi-level device assignment at 60% (x3!)

- Interrupts considered harmful, cause exit multiplication

# Macro: multi-level device assignment (sans interrupts)

- What if we could deliver device interrupts directly to L<sub>2</sub>?

- Only 7% difference between native and nested guest!

### Micro: synthetic worst case CPUID loop

- CPUID running in a tight loop is not a real-world workload!

- Went from 30x worse to "only" 6x worse

- A nested exit is still expensive—minimize both single exit cost and frequency of exits

### Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some

workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles? It's turtles all the way down

10 28/30

- Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles? It's turtles all the way down

- Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles? It's turtles all the way down

- Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles? It's turtles all the way down

- Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles?

It's turtles all the way down

- Efficient nested x86 virtualization is challenging but feasible

- A whole new ballpark opening up many exciting applications—security, cloud, architecture, ...

- Current overhead of 6-14%

- Negligible for some workloads, not yet for others

- Work in progress—expect at most 5% eventually

- Code is available

- Why Turtles? It's turtles all the way down

### Questions?

IBM

# IBM Research – Haifa is hiring

#### Systems Software Research in Haifa

- Contributions to IBM products, cutting-edge research Virtualization, Cloud Computing, Data Storage

- Influencing European cloud research agenda

- Consulting to European Commission, working through industrial groups, leading projects

- Papers, patents, image for IBM and Israel

- We are Hiring!

- Researchers and Engineers

#### SYSTOR 2009 The Israeli Experimental Systems Conference

May 4.6, 2009 Organized by IBM R&D Labs in Israel

IBM Haifa Research Lab and IBM Systems and Technology Group Lab. Israeli academia, are organizing SYSTOR 2009, a successor to the hig workshops on systems and storage held at the IBM Haifa Research La conference is to promote systems research and to foster stronger ties worldwide systems research communities and industry.

May 24-26, 2010 Haifa, Israel

The Turtles Project: Nested Virtualization

Linu